University of South Florida Scholar Commons

Graduate Theses and Dissertations

**Graduate School**

3-3-2010

# Probabilistic Error Analysis Models for Nano-Domain VLSI Circuits

Karthikeyan Lingasubramanian University of South Florida

Follow this and additional works at: https://scholarcommons.usf.edu/etd

#### **Scholar Commons Citation**

Lingasubramanian, Karthikeyan, "Probabilistic Error Analysis Models for Nano-Domain VLSI Circuits" (2010). *Graduate Theses and Dissertations.* https://scholarcommons.usf.edu/etd/1699

This Dissertation is brought to you for free and open access by the Graduate School at Scholar Commons. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of Scholar Commons. For more information, please contact scholarcommons@usf.edu.

#### Probabilistic Error Analysis Models for Nano-Domain VLSI Circuits

by

Karthikeyan Lingasubramanian

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering Department of Electrical Engineering College of Engineering University of South Florida

Major Professor: Sanjukta Bhanja, Ph.D. Nagarajan Ranganathan, Ph.D. Syed M. Alam, Ph.D. Wilfrido A. Moreno, Ph.D. Paris H. Wiley, Ph.D.

> Date of Approval: March 3, 2010

Keywords: Reliability, Worst-case input, Sequential circuits, Redundancy models

© Copyright 2010, Karthikeyan Lingasubramanian

## DEDICATION

To my Family and Friends

#### ACKNOWLEDGEMENTS

I would like to thank my major professor Dr. Sanjukta Bhanja for believing in me and for giving me this opportunity. Without her support this dissertation wouldn't have been possible. She has trained me in every aspect of research and has helped me mold myself as a better researcher. Moreover she has also been a good friend to me.

My sincere thanks to Dr. Nagarajan Ranganathan, Dr. Syed M. Alam, Dr. Wilfredo A. Moreno and Dr. Paris H. Wiley for serving in my committee. I would like to thank them all for their valuable support and advice and most importantly for allotting their time in spite of their busy schedule.

I would like to thank all the faculties and staff of the Department of Electrical Engineering and College of Engineering.

I would like to thank all my present and former colleagues, Javier, Anitha, Srinath, Dinuka, Jose, Pruthvi, Thara, Shiva, Nirmal, Vivek, Satish, Praveen and Saket, for their unconditional support.

I am really very grateful for the invaluable support and motivation that I received from my family.

I would also like to thank all my friends that I ever had in my whole life.

## TABLE OF CONTENTS

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                  |                                        |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                 | v                                      |  |

| ABSTRACT                                                                                                                                                                                                                                                                                                                                                        | viii                                   |  |

| CHAPTER 1INTRODUCTION1.1Motivation1.2Significance1.3Contribution1.4Scope of Application1.5Organization                                                                                                                                                                                                                                                          | 1<br>2<br>3<br>5<br>8<br>10            |  |

| CHAPTER 2 RELATED WORK<br>2.1 SEU Modeling<br>2.2 Dynamic Error Modeling<br>2.2.1 Calculation of Error Bounds<br>2.2.2 Calculation of Average Error<br>2.2.3 Error Reduction Through Redundancy<br>2.3 Relation to State-of-the-Art                                                                                                                             | 12<br>12<br>13<br>13<br>16<br>19<br>22 |  |

| <ul> <li>CHAPTER 3 DESIGN FUNDAMENTALS</li> <li>3.1 Probabilistic Representation of Digital Circuits</li> <li>3.2 Modeling Error in Digital Circuits</li> </ul>                                                                                                                                                                                                 | 24<br>24<br>29                         |  |

| <ul> <li>CHAPTER 4 MAXIMUM ERROR MODELING</li> <li>4.1 Maximum a Posteriori (MAP) Estimate</li> <li>4.1.1 Calculation of MAP Upper Bounds Using Shenoy-Shafer Algorithm</li> <li>4.1.2 Calculation of the Exact MAP Solution</li> <li>4.1.3 Calculating the Maximum Output Error Probability</li> <li>4.1.4 Computational Complexity of MAP Estimate</li> </ul> | 33<br>35<br>38<br>52<br>55<br>55       |  |

| <ul> <li>4.2 Experimental Results</li> <li>4.2.1 Experimental Procedure for Calculating Maximum Output Error<br/>Probability</li> </ul>                                                                                                                                                                                                                         | 56<br>56                               |  |

i

|         | 4.2.2     | Worst-case Input Vectors                                          | 58  |

|---------|-----------|-------------------------------------------------------------------|-----|

|         | 4.2.3     | Circuit-Specific Error Bounds for Fault-Tolerant Computation      | 59  |

|         | 4.2.4     | Validation Using HSpice Simulator                                 | 61  |

|         | 4.2.5     | Results with Multiple $\varepsilon$                               | 65  |

| 4.3     | Discussi  | lon                                                               | 66  |

| CHAPTER | 5 MO      | DELING ERROR IN SEQUENTIAL CIRCUITS                               | 67  |

| 5.1     | Sequent   | ial Logic Model                                                   | 68  |

|         | 5.1.1     | TDM Model                                                         | 69  |

| 5.2     | Error M   | odel                                                              | 70  |

|         | 5.2.1     | Structure                                                         | 70  |

|         | 5.2.2     | Inference Scheme                                                  | 74  |

|         | 5.2.3     | Output Error Probability                                          | 78  |

| 5.3     | Experim   | nental Results                                                    | 78  |

|         | 5.3.1     | Experimental Procedure                                            | 79  |

|         | 5.3.2     | Output Error Probabilities                                        | 80  |

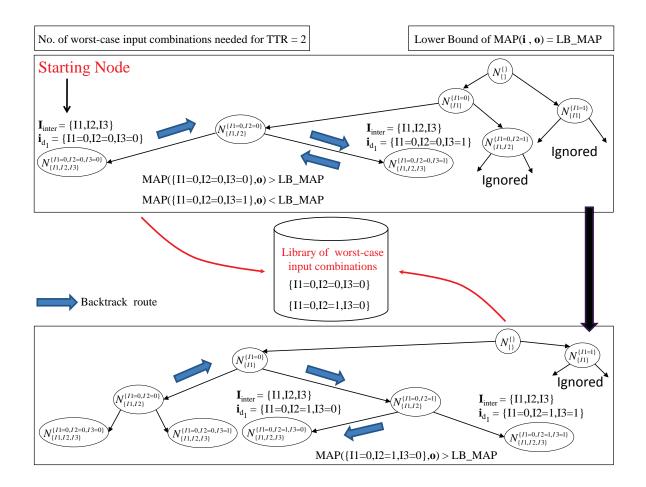

|         | 5.3.3     | Number of Time Slices                                             | 80  |

|         | 5.3.4     | 1 10                                                              | 81  |

|         | 5.3.5     | Output Error Probabilities for $\varepsilon_0 \neq \varepsilon_1$ | 83  |

|         | 5.3.6     | Validation Using HSpice Simulation                                | 84  |

| 5.4     | Discussi  | on                                                                | 85  |

| CHAPTER | 6 REI     | DUNDANCY SCHEMES FOR ERROR MITIGATION                             | 86  |

| 6.1     | Tempora   | al Redundancy Scheme Using Triple Temporal Redundancy (TTR)       |     |

|         | Techniq   | ue                                                                | 87  |

|         | 6.1.1     | Determination of the Set of Worst-Case Input Combinations for     |     |

|         |           | Selective Redundancy in TTR                                       | 87  |

|         | 6.1.2     | Experimental Setup for TTR                                        | 89  |

| 6.2     | Spatial H | Redundancy Scheme Using Cascaded Triple Modular Redundancy        |     |

|         | (CTMR)    | ) Technique                                                       | 93  |

|         | 6.2.1     | Sensitivity Analysis for Selective Redundancy in CTMR             | 94  |

| 6.3     | Hybrid l  | Redundancy                                                        | 94  |

| 6.4     | Experim   | nental Results                                                    | 95  |

|         | 6.4.1     | Error Mitigation Through Temporal Redundancy                      | 96  |

|         | 6.4.2     | Error Mitigation Through Spatial Redundancy                       | 97  |

|         | 6.4.3     | Error Mitigation Through Hybrid Redundancy                        | 98  |

|         | 6.4.4     | Comparison Between the Redundancy Schemes                         | 99  |

|         | 6.4.5     | Error Mitigation Through Hybrid Redundancy with Different         |     |

|         |           | Combinations of Spatial and Temporal Redundancies                 | 101 |

|         | 6.4.6     | Delay and Area Penalties                                          | 102 |

| 6.5     | Discussi  | on                                                                | 103 |

| CHAPTER | 7 COI     | NCLUSION AND FUTURE DIRECTIONS                                    | 104 |

ii

#### REFERENCES

## ABOUT THE AUTHOR

End Page

106

### LIST OF TABLES

| Table 4.1. | Valuations of the variables derived from corresponding CPTs                                                                        | 40 |

|------------|------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 4.2. | Combination                                                                                                                        | 41 |

| Table 4.3. | Worst-case input vectors from MAP                                                                                                  | 58 |

| Table 4.4. | Run times for MAP computation                                                                                                      | 61 |

| Table 4.5. | Comparison between maximum error probabilities achieved from the proposed model and the HSpice simulator at $\epsilon = 0.05$      | 62 |

| Table 5.1. | Conditional probabilistic tables for error-free and error-prone NAND logic                                                         | 73 |

| Table 5.2. | Conditional probabilistic table for error-prone NAND logic having variable gate error probabilities, $\epsilon_0$ and $\epsilon_1$ | 73 |

| Table 5.3. | Output error probabilities at $\epsilon = 0.001, 0.003, 0.005, 0.01$                                                               | 80 |

| Table 5.4. | Output error probabilities at $\varepsilon = 0.001, 0.003, 0.005, 0.01$ compared with HSpice simulation results                    | 84 |

## LIST OF FIGURES

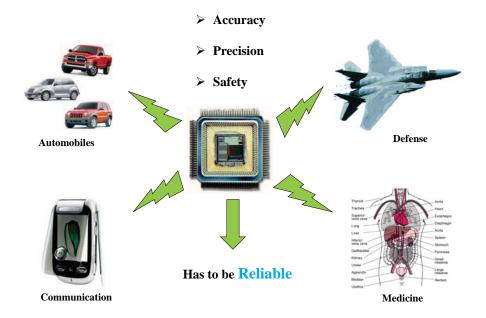

| Figure 1.1. | Significance of this dissertation                                                                                             | 4  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2. | Scope of application                                                                                                          | 8  |

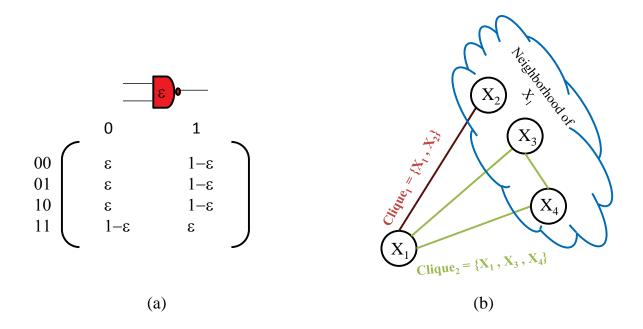

| Figure 2.1. | (a) Probabilistic transfer matrix for erroneous NAND gate with error probability $\epsilon$ [45] (b) Markov random field [47] | 17 |

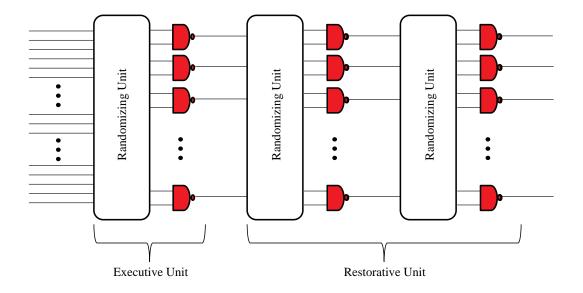

| Figure 2.2. | NAND multiplexing scheme introduced by Von Neumann [1]                                                                        | 20 |

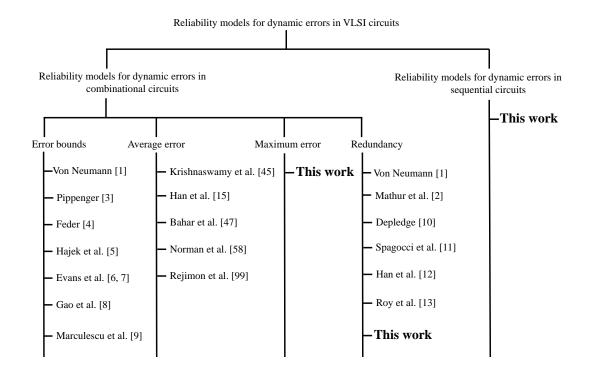

| Figure 2.3. | Some of the related works on reliability models for dynamic errors in VLSI circuits                                           | 22 |

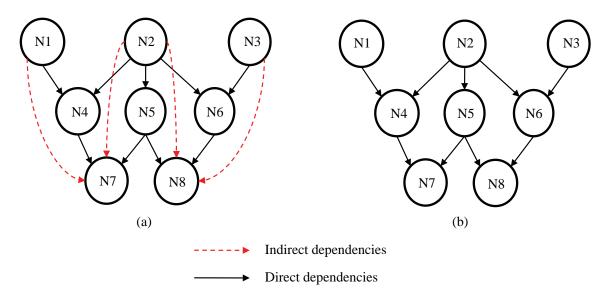

| Figure 3.1. | Representation of a digital circuit as a probabilistic graph                                                                  | 25 |

| Figure 3.2. | Minimal representation of the probabilistic graph                                                                             | 27 |

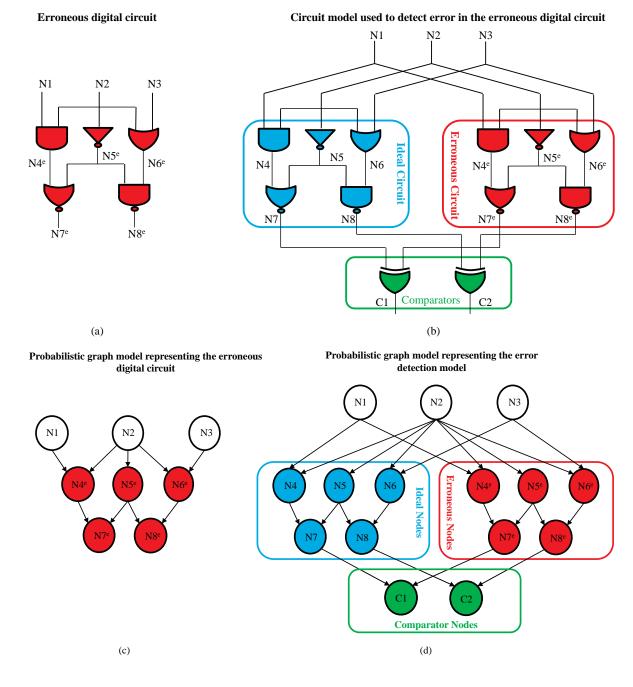

| Figure 3.3. | Error model                                                                                                                   | 30 |

| Figure 3.4. | Conditional probabilistic tables for the ideal and erroneous nodes in the error model                                         | 31 |

| Figure 4.1. | (a) Digital logic circuit (b) Error model (c) Probabilistic error model                                                       | 36 |

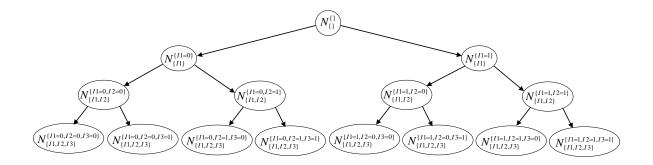

| Figure 4.2. | Search tree where depth first branch and bound search performed                                                               | 38 |

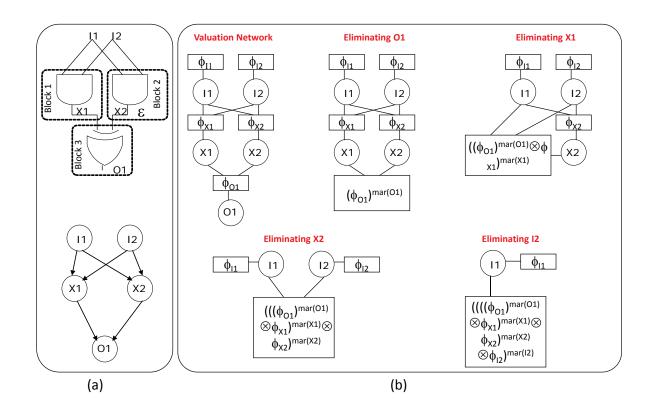

| Figure 4.3. | Illustration of the fusion algorithm                                                                                          | 41 |

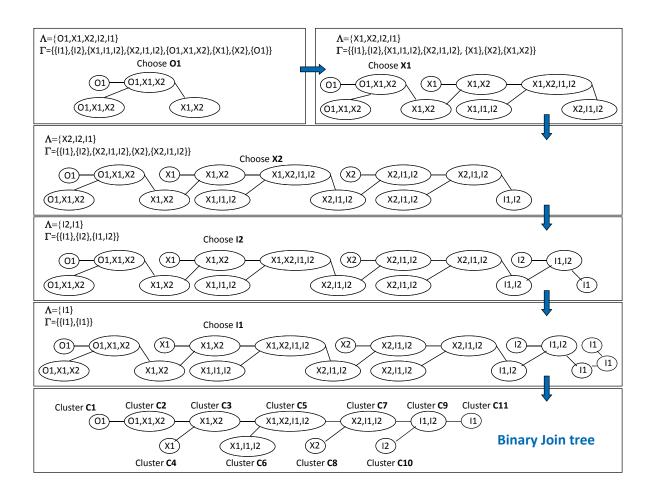

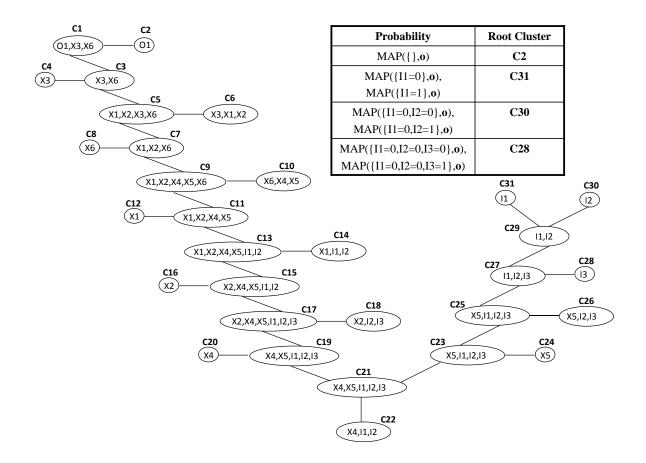

| Figure 4.4. | Partial illustration of binary join tree construction method for the first chosen variable                                    | 44 |

| Figure 4.5. | Complete illustration of binary join tree construction method                                                                 | 45 |

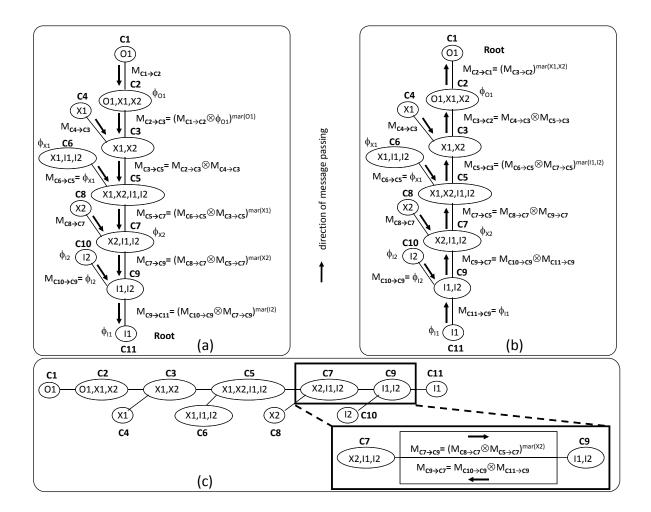

| Figure 4.6. | (a) Message passing with cluster C11 as root (b) Message passing with cluster C1 as root (c) Message storage mechanism        | 47 |

| Figure 4.7. | Binary join tree for the probabilistic error model in Fig. 4.1.(c)                                                            | 51 |

| Figure 4.8. | Search process for MAP computation                                                                                            | 53 |

v

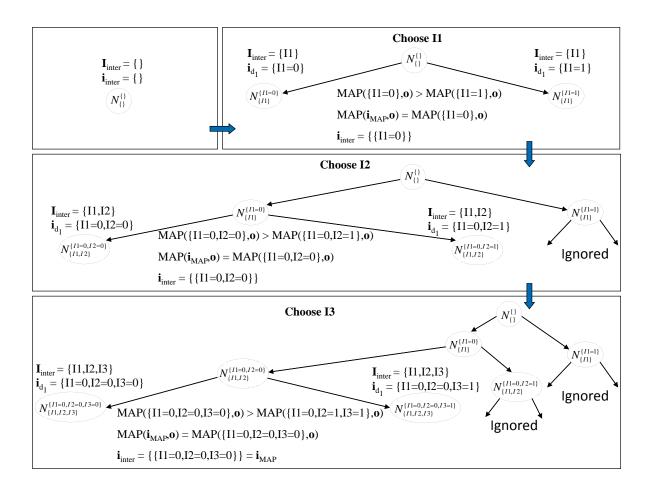

| Figure 4.9.  | Flow chart describing the experimental setup and process                                                                                                                                                                                                                                        | 57 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

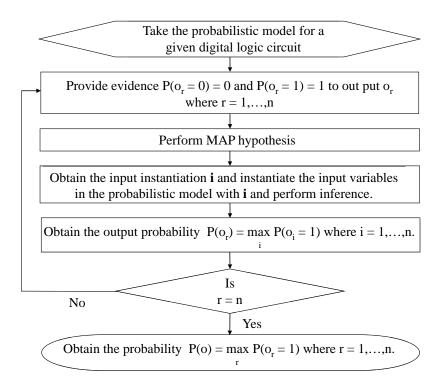

| Figure 4.10. | Circuit-specific error bound along with comparison between maximum and average output error probabilities for (a) $c17$ , (b) $max_flat$ , (c) <i>voter</i> , (d) <i>pc</i> , (e) <i>count</i> , (f) <i>alu</i> 4, (g) <i>malu</i> 4                                                            | 60 |

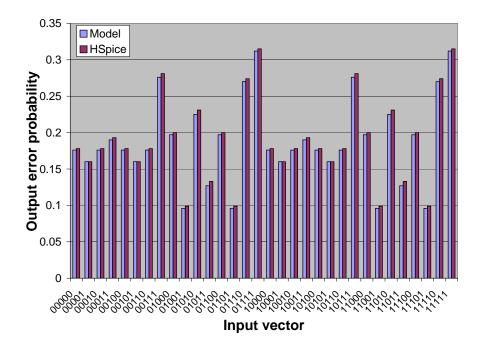

| Figure 4.11. | Output error probabilities for the entire input vector space with gate error probability $\varepsilon = 0.05$ for $c17$                                                                                                                                                                         | 63 |

| Figure 4.12. | (a) Output error probabilities $\geq (\mu + \sigma)$ , calculated from probabilistic error model, with gate error probability $\varepsilon = 0.05$ for <i>max_flat</i> (b) Corresponding HSpice calculations                                                                                    | 64 |

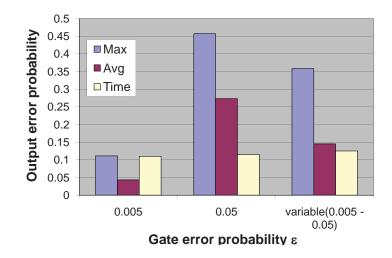

| Figure 4.13. | Comparison between the average and maximum output error probability<br>and run time for $\varepsilon$ =0.005, $\varepsilon$ =0.05 and variable $\varepsilon$ ranging from 0.005 -<br>0.05 for <i>max_flat</i>                                                                                   | 65 |

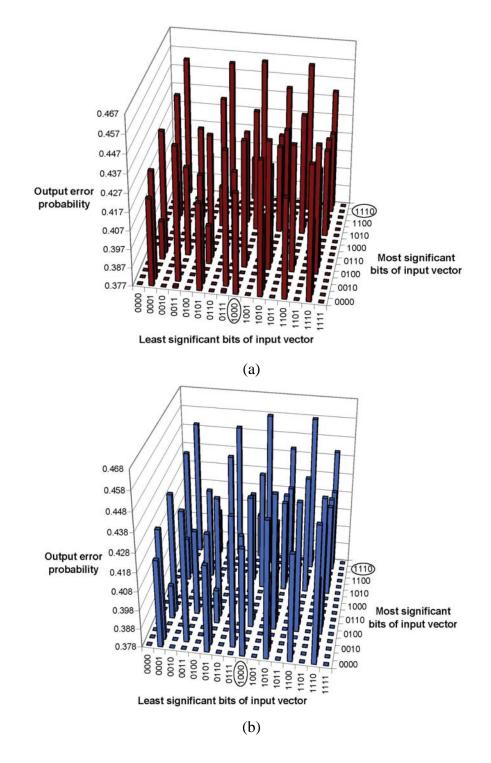

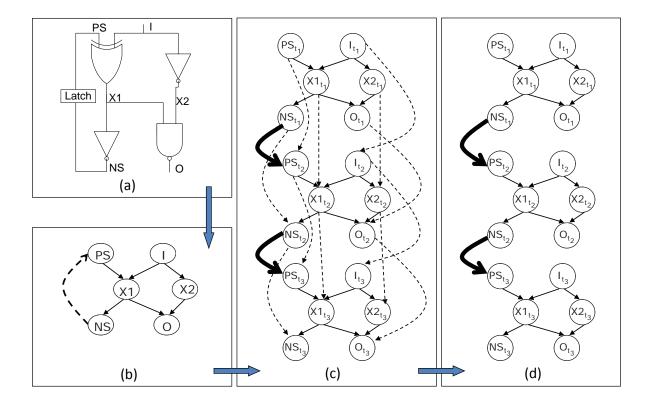

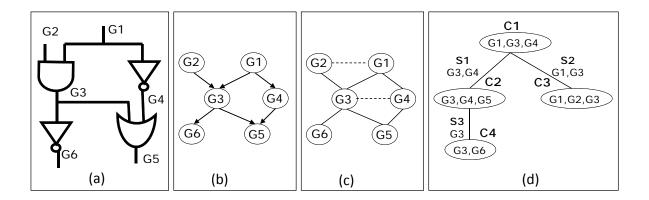

| Figure 5.1.  | (a) Digital logic circuit (b) Corresponding probabilistic model (c) DAG representation which is not minimal (d) TDM model                                                                                                                                                                       | 68 |

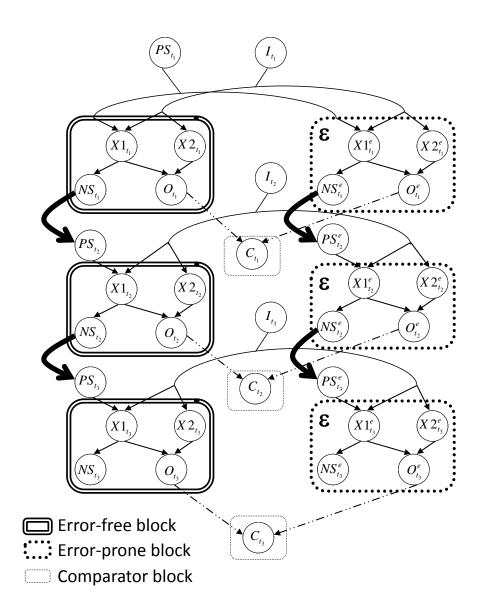

| Figure 5.2.  | Error model obtained from TDM model with 3rd order temporal depen-<br>dence                                                                                                                                                                                                                     | 71 |

| Figure 5.3.  | (a) Digital logic circuit (b) Corresponding probabilistic model (c) Moral graph obtained by adding undirected links between parents of common child nodes (d) Corresponding join tree obtained                                                                                                  | 76 |

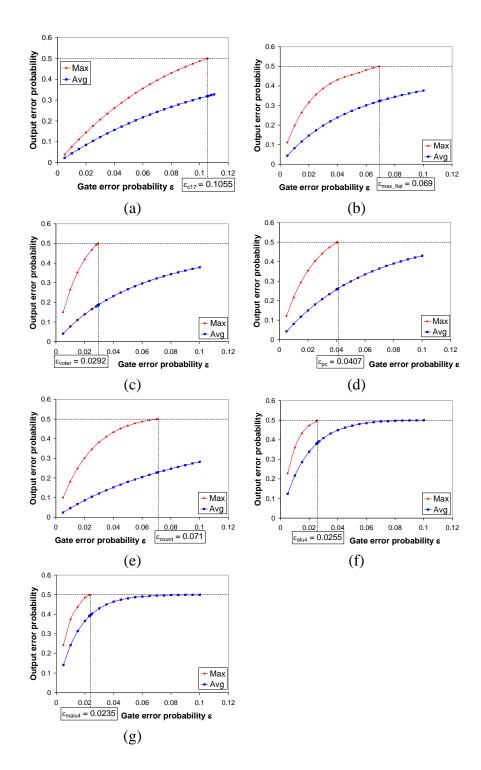

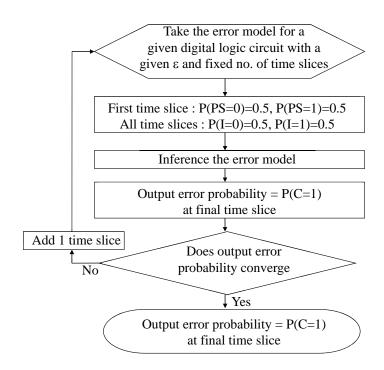

| Figure 5.4.  | Flowchart for experimental procedure                                                                                                                                                                                                                                                            | 79 |

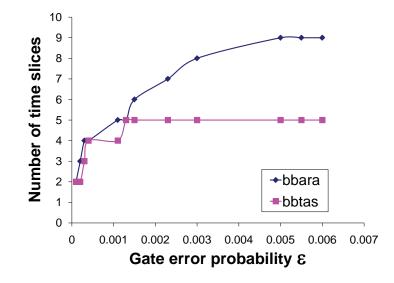

| Figure 5.5.  | Number of time slices needed by <i>bbara</i> and <i>bbtas</i> for $\varepsilon = 0 - 0.006$                                                                                                                                                                                                     | 81 |

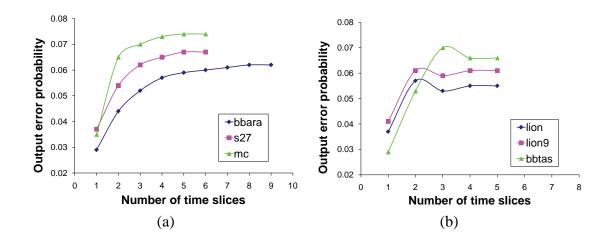

| Figure 5.6.  | (a) Transition of output error probability across time slices for <i>bbara</i> , <i>s</i> 27 and <i>mc</i> with $\varepsilon = 0.01$ (b) Transition of output error probability across time slices for <i>lion</i> , <i>lion</i> 9 and <i>bbtas</i> with $\varepsilon = 0.01$                   | 82 |

| Figure 5.7.  | (a) Transition of error-free and error-prone output probabilities across time slices for <i>bbtas</i> , <i>lion</i> 9 and <i>lion</i> with $\varepsilon = 0.01$ (b) Transition of error-free and error-prone output probabilities across time slices for <i>bbara</i> with $\varepsilon = 0.01$ | 82 |

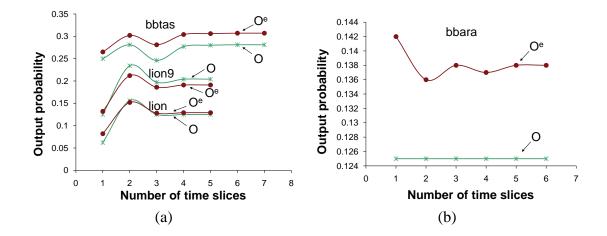

| Figure 5.8.  | Output error probabilities for ( $\epsilon_0=0.01,\ \epsilon_1=0.02$ ) and ( $\epsilon_0=0.02,\ \epsilon_1=0.01$ )                                                                                                                                                                              | 83 |

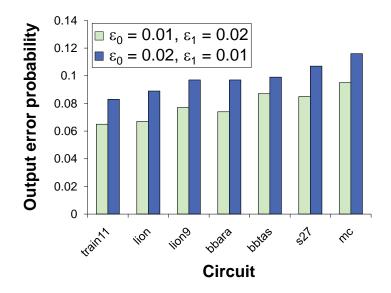

| Figure 6.1.  | Determination of the set of worst-case input combinations by backtrack-<br>ing through the search tree used for MAP computation given in Fig. 4.8.                                                                                                                                              | 88 |

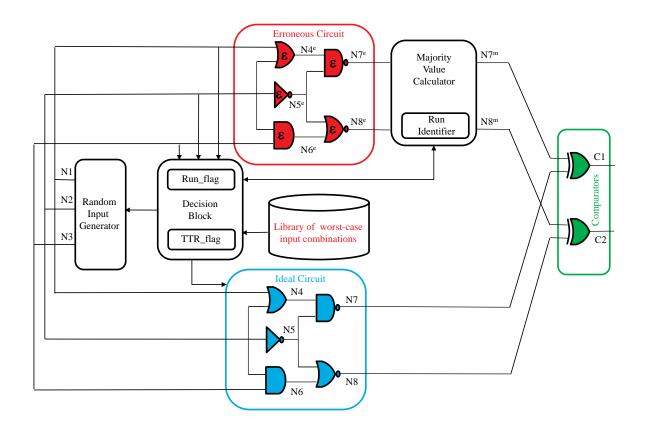

| Figure 6.2.  | Experimental setup for TTR incorporating selective redundancy                                                                                                                                                                                                                                   | 90 |

|              |                                                                                                                                                                                                                                                                                                 |    |

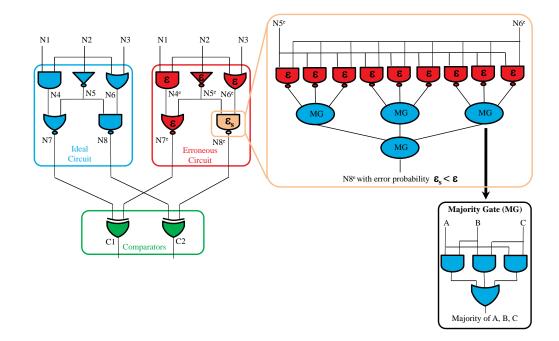

| Figure 6.3.  | Spatial redundancy scheme using CTMR technique incorporating majority logic                                                                                       | 94  |

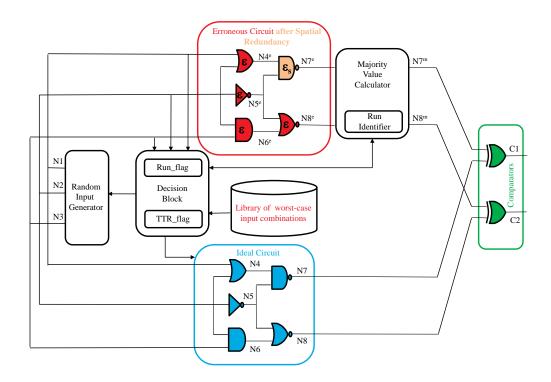

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 6.4.  | Hybrid redundancy scheme using CTMR and TTR techniques                                                                                                            | 95  |

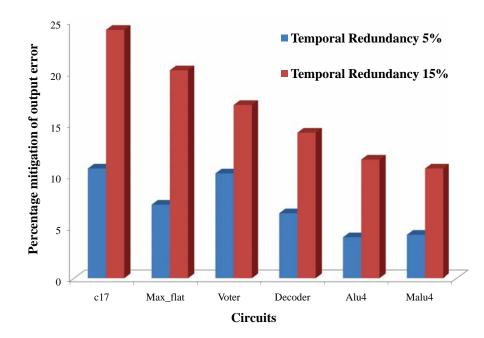

| Figure 6.5.  | Percentage mitigation of output error achieved through 5% and 15% temporal redundancy with $\epsilon$ =0.001                                                      | 96  |

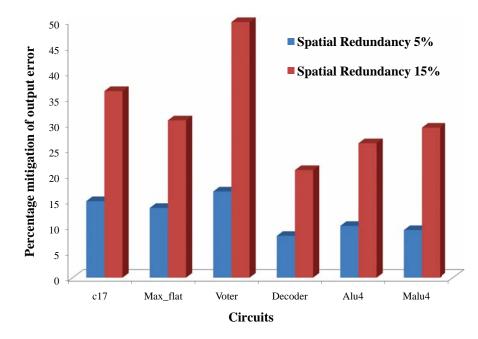

| Figure 6.6.  | Percentage mitigation of output error achieved through 5% and 15% spatial redundancy with $\epsilon$ =0.001                                                       | 98  |

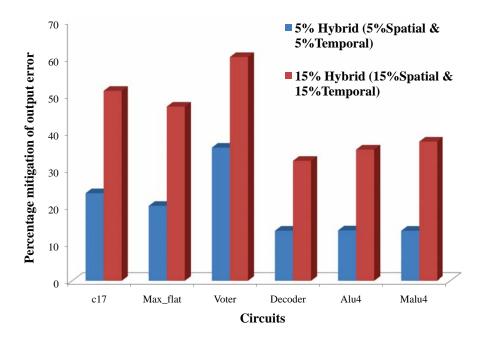

| Figure 6.7.  | Percentage mitigation of output error achieved through 5% and 15% hybrid redundancy with $\epsilon$ =0.001                                                        | 99  |

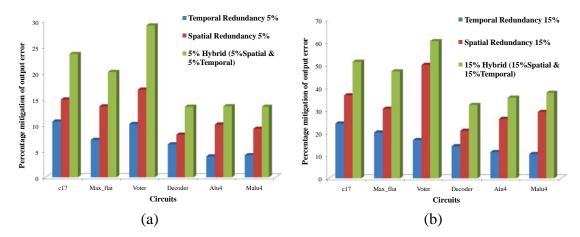

| Figure 6.8.  | Comparison between the redundancy schemes for (a) 5% and (b) 15% redundancy with $\epsilon{=}0.001$                                                               | 100 |

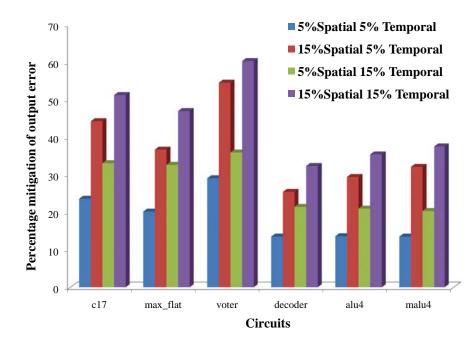

| Figure 6.9.  | Percentage mitigation of output error achieved through hybrid redundancy with different combinations of spatial and temporal redundancies while $\epsilon$ =0.001 | 101 |

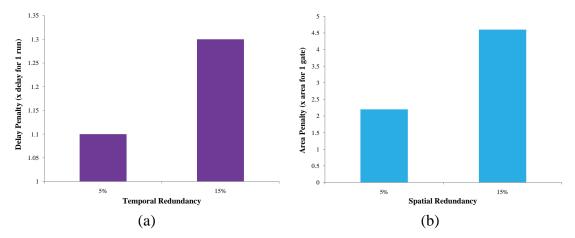

| Figure 6.10. | (a) Delay penalty in temporal redundancy (b) Area penalty in spatial redundancy                                                                                   | 102 |

vii

#### PROBABILISTIC ERROR ANALYSIS MODELS FOR NANO-DOMAIN VLSI CIRCUITS

#### Karthikeyan Lingasubramanian

#### ABSTRACT

Technology scaling to the nanometer levels has paved the way to realize multi-dimensional applications in a single product by increasing the density of the electronic devices on integrated chips. This has naturally attracted a wide variety of industries like medicine, communication, automobile, defense and even house-hold appliance, to use high speed multi-functional computing machines. Apart from the advantages of these nano-domain computing devices, their usage in safety-centric applications like implantable biomedical chips and automobile safety has immensely increased the need for comprehensive error analysis to enhance their reliability. Moreover, these nano-electronic devices have increased propensity to transient errors due to extremely small device dimensions and low switching energy. The nature of these transient errors is more probabilistic than deterministic, and so requires probabilistic models for estimation and analysis. In this dissertation, we present comprehensive analytic studies of error behavior in nano-level digital logic circuits using probabilistic reliability models. It comprises the design of exact probabilistic error models, to compute the *maximum* error over all possible input space in a circuit-specific manner; to study the behavior of transient errors in sequential circuits; and to achieve error mitigation through redundancy techniques. The model to compute maximum error, also provides the worst-case input vector, which has the highest probability to generate an erroneous output, for any given logic circuit. The model for sequential logic that can measure the expected output error probability, given a probabilis-

viii

tic input space, can account for both spatial dependencies and temporal correlations across the logic, using a time evolving causal network. For comprehensive error reduction in logic circuits, temporal, spatial and hybrid redundancy models, are implemented. The temporal redundancy model uses the triple temporal redundancy technique that applies redundancy in the input space, spatial redundancy model uses the cascaded triple modular redundancy technique that applies redundancy in the intermediate signal space and the hybrid redundancy techniques encapsulates both temporal and spatial redundancy schemes. All the above studies are performed on standard benchmark circuits from ISCAS and MCNC suites and the subsequent experimental results are obtained. These results clearly encompasses the various aspects of error behavior in nano VLSI circuits and also shows the efficiency and versatility of the probabilistic error models.

## CHAPTER 1 INTRODUCTION

Integrated Circuits are used in a wide range of important applications like automobile, aircraft, medicine, defense, communication and even house-hold appliances. Critical applications like medicine demand high accuracy and efficiency due to stringent safety requirements, while applications like automotive, defense demand more robustness due to extreme working conditions [41, 42, 39]. Also the demand for multi-dimensional applications in a single product has increased the density of the electronic devices on a chip eventually resulting in reduction of device feature size, pushing the technology to nanometer levels [60, 59]. Complementary Metal Oxide Semiconductor (CMOS) transistors, which are the current generation electronic devices, have been shrunk to sub-50nm dimensions [59]. This reduction in feature size results in variations in device and process parameters, which in turn leads to transient dynamic faults in digital circuits. In this dissertation, we present an error model that can handle these transient dynamic faults using probabilistic methods. Using this error model, we present a unique method to calculate maximum errors in digital circuits. Also, based on this error model, we present a time evolving probabilistic network that can calculate error in sequential circuits. Finally, we present temporal, spatial and hybrid redundancy techniques, which incorporates selective redundancy using the base error model, for error mitigation in digital circuits.

1

#### 1.1 Motivation

*Why use probabilistic models?* Nano-domain computing devices are likely to have higher error rates (both in terms of defect and transient faults) as they operate near the thermal limit and information processing occurs at extremely small volume [61, 47]. Nano-CMOS, beyond 22nm, is not an exception in this regard as the frequency scales up and voltage and geometry scales down. The resulting errors, due to uncontrollable variations in device and process parameters like temperature and threshold voltage, are highly intractable for deterministic testing tools used to detect permanent faults. A fresh look at reliability in a technology independent fashion is both timely and necessary. Given the inherent stochastic nature of the devices in the nano-regime, instead of deterministic logic models probabilistic models would be more appropriate. This requires a significant shift in the design and testing paradigm, with reliability adopting a central role in design of electronic devices.

Why model maximum error? Industries like automotive and health care have traditionally addressed high reliability requirements by employing redundancy, error corrections, and choice of proper assembly and packaging technology. In addition, rigorous product testing at extended stress conditions filters out even an entire lot in the presence of a small number of failures [39]. Another rapidly growing class of electronic chips where reliability is very critical is implantable biomedical chips [41, 42]. More interestingly, some of the safety approaches, such as redundancy and complex packaging, are not readily applicable to implantable biomedical applications because of low voltage and low power operation and small form factor requirements. Authors in [41] identified that conventional approaches in device and parasitic modeling, circuit techniques, and manufacturing and test need to improve due to extreme low power and high reliability requirements, since these constraints pose serious complexities in circuit design through unpredictable design environment. In addition, we believe our method of calculating maximum probability of error and the proposed maximum

error probability aware design is well suited for implantable biomedical IC design. While two design implementation choices can have different average probabilities of failures, the lower average choice may in fact have higher maximum probability of failure leading to lower yield in manufacturing and more rejects during chip burn-in and extended screening. Also, when the input space for a circuit is completely random and equally probable, calculation of average error will suffice. But, as in some cases, when the input space gets biased, the average error information will not be comprehensive enough to understand the error behavior in the circuit. Therefore, using maximum probability of failure as a critical design metric along with average case would be required in design of safety critical electronic chips.

Why model error in sequential circuits? Most of the real-time applications of electronic devices, like random access memories, needs them to be sequential in nature. Sequential circuits consist of a combinational logic block, set of inputs, set of state bits where the values of the next state bit is fed back to the present state in the next clock cycle through latches. At a given time instance  $t_i$ , the state signals  $s_{t_i}$  are uniquely identified as a function of primary input signals  $i_{t_i}$  and state signals  $s_{t_{i-1}}$  of the previous time instance giving rise to temporal correlations. Due to this, error occurring in the combinational part of the circuit at one time instance might propagate towards several consecutive time instances making the device more vulnerable [54, 51]. The static reliability models used for combinational circuits are not adequate to model the temporal dependencies between the circuit nodes, at the combinational part of the sequential circuit, at different time instances [52, 53, 54, 51, 55]. In order to handle this a more dynamic model which can evolve through consecutive time instances is needed.

#### 1.2 Significance

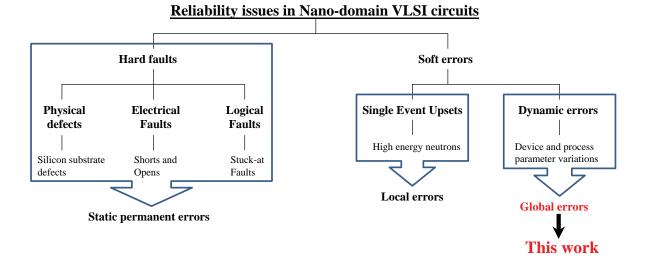

The errors that can occur in nano-domain VLSI circuits can be widely divided into two categories, *hard faults* and *soft errors*. Hard faults refer to any permanent faults that can

Figure 1.1. Significance of this dissertation

occur in a circuit component due to physical defects like oxide abnormalities in the transistor, electrical defects like shorts and opens, logical defects like stuck-at and delay faults. Soft errors refer to the failures in circuit components due to external conditions like high energy neutron interaction or device parameter variations. Out of these categories, soft errors are the toughest to model due to their transient nature, since the external conditions responsible for these errors are highly unpredictable at the nanometer levels. So, the reliability models used to address hard faults cannot be used to model soft errors, since they are completely deterministic. Therefore, comprehensive probabilistic models, like our model, are well suited to handle the transient soft errors.

The most prevalent soft errors in nano-domain VLSI circuits are widely categorized into Single Event Upsets (SEUs) due to external particle interaction, and dynamic errors due to device and process variabilities. While failures due to SEUs are more localized, in the sense, they occur in a particular component in the circuit and gets propagated, dynamic errors are more global, in the sense that, they can occur on multiple components of the circuit at the same time. So, the models that address failures due to SEUs are not enough to model dynamic

errors. Our model, presented in this work, targets the dynamic errors by giving provisions to address error behavior in multiple circuit components at the same time.

Also our model can be considered as a complete and comprehensive model that can accurately calculate *both maximum and average errors* in digital circuits. This versatility offers a wider diagnostic application space, which aids the collection of a variety of information sets that are highly essential for IC testing.

#### 1.3 Contribution

The contributions of this dissertation are as follows,

- A method to calculate *maximum* output error in digital circuits using a probabilistic model is presented.

- Given a circuit with a fixed gate error probability ε, this error model can provide the maximum output error probability and the worst-case input vector, which can be very useful testing parameters. Its also shown that these worst-case input vectors not only depend on the circuit structure but could dynamically change with ε.

- It is shown that the maximum output error probabilities are much larger than average output error probabilities, for comparatively lower values of individual gate error probability ε, thereby signifying the importance of maximum error as a design parameter.

- The circuit-specific error bounds for fault-tolerant computation are presented and it is shown that maximum output errors provide a tighter bound. Also, it is shown that the error bound for an individual gate placed in a circuit can be dependent on the circuit structure.

- Through this work, an efficient design framework that employs inference in binary join trees using *Shenoy-Shafer* algorithm, to perform MAP hypothesis accurately, is being applied for the first time in the context of digital computing machines.

- The validity of the error model is tested through comparison with circuit simulations using HSpice and the results showed that the highest % difference of the error model over HSpice is just 1.23%, signifying its accuracy.

- The possibility of efficient error incorporation in this model is presented by providing variable ε values to different gates of a circuit, instead of providing the same ε value to all gates. This formation of the error model can help in useful diagnostic studies like error sensitivity analysis.

- An exact probabilistic error model that can study transient error behavior in *sequential* logic is presented.

- This model can accurately calculate the average output error probability in any given sequential circuit.

- A *minimal* time evolving probabilistic network, namely, the Temporal Dependency Model (TDM), that can handle both spatial dependencies between nodes in a single time slice and temporal dependencies between nodes in different time slices, is presented.

- It is shown that the increase in output error probabilities is more than 2 folds, even for a slight increase in ε value, thereby indicating the vulnerability of sequential circuits to transient errors.

- The crucial study of error propagation across different time instances, in a sequential circuit, can be performed using this model. This study is important to understand error behavior in sequential circuits.

- It is shown that the number of time slices needed by the model, to converge to a final average output error value, is completely dependent on the circuit structure.

- The flexibility of the error model is shown by incorporating unequal gate error probability values,  $\varepsilon_0$  and  $\varepsilon_1$ , to study the effect of  $0 \rightarrow 1$  and  $1 \rightarrow 0$  errors on the output of a circuit. Given a gate output signal,  $\varepsilon_0$  represents the probability of error occurrence when the ideal value of the signal is '0', and  $\varepsilon_1$  represents the probability of error occurrence when the ideal value of the signal is '1'.

- The validity of the error model is tested through comparison with circuit simulations using HSpice and the results showed that the highest percentage difference of the error model over HSpice is only 6.25%, signifying its accuracy.

- Using the probabilistic error model, temporal, spatial and hybrid redundancy techniques are performed, to achieve error mitigation in digital logic circuits.

- Efficient error reduction is achieved through *selective* redundancy, which is established by applying redundancy only to the most influential input combinations and the most sensitive nodes.

- Through experimental results, the relative benefits of the temporal, spatial and hybrid redundancy schemes are presented and hybrid redundancy is shown to be the best scheme for error mitigation in digital logic circuits.

- It is shown that increasing the amount of redundancy results in better error mitigation in all the three schemes.

- It is shown that the error mitigation percentage for 15% temporal redundancy, is more than 10% for all circuits, while for 15% spatial redundancy, it is more than 20% for all circuits and for 15% hybrid redundancy, it is more than 30% for all circuits, thereby showing the high yield of hybrid redundancy scheme.

7

Figure 1.2. Scope of application

Delay and area penalties in temporal and spatial redundancies respectively are presented and its is shown that the area penalty is much higher than the delay penalty.

#### **1.4 Scope of Application**

Digital VLSI circuits are widely used in critical and essential applications like automobiles, defense, medicine and communication. The need for reliable computation in these circuits are of the utmost importance due to the nature of its applications. VLSI circuits are used in the automobile brake system, implantable bio-medical devices like pacemaker, aircraft control system and multi-functional smart phones like iPhone. The scaled computational devices in current generation nano-domain VLSI circuits has immensely improved its application space. The advent of smart phones and implantable bio-medical chips are made possible primarily by this scaling trend. At the same time VLSI circuits at nano-domain suffer from various reliability issues that should be addressed during the design process.

In nano-domain digital VLSI circuits, affected by multiple errors, there can be one maximum error that can even breakdown the entire device. While primarily all of the current reliability studies estimate the overall adverse effect by considering the average of all errors, estimating the worst-case maximum error has proved to be tedious and cumbersome. Our reliability model, presented in this dissertation, can efficiently estimate this worst-case maximum error and the input vector associated with this error, through intelligent diagnostic studies.

In IC testing, the usage of a probabilistic error model and the information about the worstcase input vector can help to improve testing techniques like scan chains, burn-in test and hierarchical testing. Scan chains are widely used in Design for Test (DFT) methodologies for IC testing. The basic idea is to form a chain of flip-flops that are made scan-able and the desired test pattern can be serially inserted into the flip-flop chain. The test pattern is applied to the logic circuits driven by the flip-flop chain after which the logic circuit outputs can also be captured into the same or different flip-flop chain for serial shift-out. In such a setup, including the worst-case input vector in the test patterns can speed up the testing process, since the most hazardous behavior of the circuit-under-test can be detected with the worst-case input vector. Burn-in tests are performed to find out devices with inherent defects or manufacturing defects [44]. These devices will go faulty when subjected to high stress. The IC is subjected to long test time and stress conditions, such as extreme Vdd and temperatures, during a burn-in test. To aid the burn-in test, a probabilistic error model that can target and exercise individual device fault modes would help to expedite the failure mechanisms and to screen for inherent faults in a shorter test time. More specifically, the worst case input vectors generated according to our method is well suited for application during the burnin test. Finally, in hierarchical testing, the entire circuit-under-test is divided into several internal modules where these modules can be tested individually. Such a hierarchical division reduces the size of circuit-under-test facilitating rigorous probabilistic error analysis and the application of worst input vectors to the targeted internal modules.

9

The reliability model for error estimation in sequential circuits, presented in this dissertation, can be used to perform efficient diagnostic studies in essential real-time applications like computer memories. In these sequential circuits, for a fixed input vector, the intermediate signals can get stuck at a wrong value due to the presence of error. This could propagate across several time instances and this behavior can happen to any input vector. Such deterministic approaches provides inaccurate estimation of the error behavior in sequential circuits. Our model, which is a probabilistic reliability model, takes care of this discrepancy by treating both input and signal space in a probabilistic manner, thereby ensuring efficient diagnostic studies for reliability.

While the three error mitigation schemes, temporal, spatial and hybrid, presented in this dissertation, can be used for error optimization in any nano-domain VLSI circuit, the trade-off studies between them can provide essential application-specific information for circuit designers. If the application demands lesser area, then more importance should be given to temporal redundancy than spatial redundancy. If the application has high probability of error occurrence in the signal space than the input space, then more importance should be given to spatial redundancy than temporal redundancy. The trade-off studies presented in this dissertation, can provide information related to the above scenarios, which are crucial for circuit design.

#### 1.5 Organization

This dissertation is organized as follows,

- Chapter 2 provides the related research works done in the field of probabilistic reliability analysis for VLSI circuits.

- Chapter 3 provides the fundamental design concepts of the probabilistic error model.

10

- Chapter 4 explains, in detail, about the modeling of maximum errors in logic circuits using a probabilistic error model.

- Chapter 5 explains, in detail, about modeling of errors in sequential circuits using a dynamic time-evolving probabilistic error model.

- Chapter 6 explains, in detail, about the temporal, spatial and hybrid redundancy schemes used for error mitigation in digital logic circuits.

- Chapter 7 provides the conclusion and future directions of this work.

## CHAPTER 2 RELATED WORK

In nanometer level circuits, due to device scaling, the most prevalent and detrimental errors are soft errors that are caused mainly by external particle interactions and variations in device and process parameters. While the former results in localized failures like Single Event Upsets (SEUs), the latter leads to more global dynamic errors.

#### 2.1 SEU Modeling

The modeling of device failures due to SEUs are done in different levels of design abstraction, like device level, circuit level and gate level [62, 69, 70, 71, 73, 85, 74]. Initial work on external radiation interaction on semiconductors was done as early as 1967 [62], in which the authors proposed one dimensional drift diffusion models to study the radiation effects on semiconductor devices used widely in space applications. This work was followed by a number of significant device level models for memory elements, using numerical simulation [63, 64]. In order to handle more complex situations, which are intractable by numerical simulation models, analytic and empirical models were proposed [67]. The study of external particle interaction with semiconductor devices, which is more of a multi dimensional phenomenon, was enhanced through the advent of two dimensional and three dimensional models [65, 66], which accurately measured the charge particle drift and diffusion mechanisms. At the circuit level, SEU modeling is done by addressing circuit parameters like supply voltage, threshold voltage and clock period; and circuit characteristics like electrical masking, logical mask-

ing and latching window effects. Simulation based models like SEMM [69] and SERA [56] encapsulates these circuit aspects to provide soft error rate analysis in digital logic circuits. While optimization techniques using dual-Vdd and gate sizing are used to model SEU [70], its effects on interconnects are also modeled at the placement level [71], using simulated annealing. At the gate level, SEU modeling is based primarily on the detection of the probability of error occurrence at the gate outputs. Logical abstraction tools like binary decision diagrams are used to perform soft error rate analysis in both combinational [72] and sequential [51] circuits, while a completely probabilistic model based on Bayesian networks was used in [85] to detect SEUs in digital logic circuits. While practical experiments like injecting SEUs in chips using laser pulses to verify fault tolerance [74, 75] were performed, popular testing techniques like built-in self-test mechanism [76] were also used to study soft errors.

#### 2.2 Dynamic Error Modeling

Dynamic errors are transient soft errors caused by the uncontrollable and unpredictable fluctuations in device and process parameters due to scaling. These global errors can coexist with the local SEUs and static hard faults, and they can happen randomly at any node in the circuit, making them untraceable. The basic concept of dynamic error modeling is the assumption that every circuit component will have a finite propensity to be erroneous. Based on this idea, researchers approached dynamic error modeling problem in three broad categories, calculation of error bounds, calculation of average error, and error reduction through redundancy.

#### 2.2.1 Calculation of Error Bounds

The study of reliable computation using unreliable components was initiated by Von Neumann [1] who showed that erroneous components with some small error probability can pro-

vide reliable outputs and this is possible only when the error probability of each component is less than 1/6. In this heuristic study, Neumann represented the logic gates as automatons which are governed by logic functions. It was stated that the probability of error in the automaton and its output cannot exceed 1/2, since the system will become irrelevant at that bound. Keeping this as the basic upper bound for the probability of error in the output, the error probability of the automaton was studied through a majority organ, in which three copies of the same automaton were created and the majority of the three outputs was considered true. This arrangement was proven to reduce the error probability of the base system, and through this it was shown that the error probability of the automaton cannot be  $\geq 1/6$ , since at this upper bound the system becomes unsustainable.

This work was later enhanced by Pippenger [3] who realized Von Neumann's model using formulas for boolean functions. Here the digital logic components are realized using functions whose number of arguments relate to the number of inputs in the component. Through this arrangement, it was shown that for a function controlled by *k*-arguments, the error probability of each component should be less than (k - 1)/2k to achieve reliable computation. Through this, an interesting result was shown for 3-input components, whose error probability bound for reliable computation was 1/3, which is greater than the Von Neumann bound of 1/6, thereby creating curiosity. This work was later extended by using networks instead of formulas to realize the reliability model [4]. In [5], Hajek and Weller used the concept of formulas to show that for 3-input gates the error probability should be less than 1/6, thereby reiterating Von Neumann's bound. Later this work was extended for *k*-input gates [6] where *k* was chosen to be odd. The authors claimed that since k + 1 input gates can simulate *k* input gates, their model can be easily used to compute bounds for gates with even number of inputs. For a specific even case, Evans and Pippenger [7] showed that the maximum tolerable noise level for 2-input NAND gate should be less than  $(3 - \sqrt{7})/4 = 0.08856\cdots$ .

Later this result was reiterated by Gao et al. [8] for 2-input NAND gate, along with other results for k-input NAND gate and majority gate, using bifurcation analysis that involves repeated iterations on a function relating to the specific computational component. The probability of the output line of a NAND gate, given by Z, was associated with the probabilities of the input lines X and Y using the equation,

$$Z = (1 - \varepsilon)(1 - XY) + \varepsilon XY = (1 - \varepsilon)(2\varepsilon - 1)XY$$

(2.1)

where  $\varepsilon$  is the probability of error in the NAND gate. In order to study the error behavior, a network of NAND gates, where the output of each gate is connected to the input of at least one other gate, was created and the inputs *X* and *Y* are considered to be equally probable to be at logic '1'. The corresponding equation for this network was written as,

$$X_{i+1} = (1 - \varepsilon) + (2\varepsilon - 1)X_i^2$$

(2.2)

The initial value  $X_0$  was arbitrarily chosen and an iterative process was performed to obtain consequent  $X_i$  values. After the solution has converged, values from the last few iterations are plotted against the corresponding  $\varepsilon$  values to obtain the bi-modal graph for bifurcation analysis. This bi-modal graph clearly showed that reliable computing using erroneous 2-input NAND gates is not possible when its error probability  $\varepsilon = 0.08856\cdots$ .

While there exist studies of circuit-specific bounds for circuit characteristics like switching activity [9], the study of circuit-specific error bounds would be highly informative and useful for designing high-end computing machines.

#### 2.2.2 Calculation of Average Error

Many researchers are currently focusing on computing the average error from a circuit and also on the expected error to conduct reliability-redundancy trade-off studies. In [45], a Probabilistic Transfer Matrix (PTM) based model for reliability studies was proposed. In this method each circuit signal is represented using random variables and the functionality of each erroneous gate is represented in a matrix form using the PTMs (Fig. 2.1.(a)). Each gate in the underlying digital circuit was represented by an individual PTM. To calculate the error probability of the circuit, a PTM for the entire circuit is formed by multiplying the individual gate PTMs. If gates  $g_1$  and  $g_2$  are connected in series, under the condition that when  $g_1$  gets an input  $g_1^I$  it results in  $g_2$  giving an output  $g_2^O$ , the combined PTM can be written as

$$p(g_2^O|g_1^I) = \sum_{allj} p(g_2^O|j) p(j|g_1^I)$$

(2.3)

If gates  $g_1$  and  $g_2$  are connected in parallel, under the condition that when  $g_1$  gets an input  $g_1^I$  it results in output  $g_1^O$  and when  $g_2$  gets an input  $g_2^I$  it results in output  $g_2^O$ , the combined PTM can be written as

$$p(g_2^O|g_1^I) = p(g_2^O|g_2^I)p(g_1^O|g_1^I)$$

(2.4)

This is an exact method but it is computationally expensive.

An approximate method based on Probabilistic Gate Model (PGM) is discussed by Han et al. in [15]. Here the PGMs are formed using the sum of product equations governing the functionality between an input and an output. For any gate, with an output  $Z_i$  and with error probability  $\varepsilon$ , its PGM can be written as,

$$Z_i = E_i(1-\varepsilon) + (1-E_i)\varepsilon \tag{2.5}$$

Figure 2.1. (a) Probabilistic transfer matrix for erroneous NAND gate with error probability  $\epsilon$  [45] (b) Markov random field [47]

where  $E_i$  is the sum of product equation. For a 2-input AND gate with inputs  $I_1$  and  $I_{12}$ ,  $E_i = I_1 I_2$ . So the corresponding  $Z_i$  can be written as,

$$Z_i = (I_1 I_2)(1 - \varepsilon) + (1 - (I_1 I_2))\varepsilon$$

(2.6)

All the gates in the circuit were represented with individual PGMs and the overall reliability of the circuit was calculated by multiplying the individual gate reliabilities, which were assumed to be independent. This approximate model was proved to be faster than the exact PTM model.

A Markov Random Field (MRF) based probabilistic model for reliability studies was proposed in [47], which concentrated more on hard errors than soft errors. Here, the circuit signals were represented as random variables in a Markov random network, where every node is dependent only with the directly connected nodes that are called its neighbors (Fig. 2.1.(b)). Given a set of random variables  $\Gamma = \{X_1, \dots, X_n\}$  forming a Markov network, the probability

of any random variable,  $X_i$ , in the Markov network was described using Gibbs distribution as follows,

$$P(X_i | \{ \Gamma - X_i \}) = \frac{1}{Z} e^{-\frac{1}{kT} \sum_{c \in \phi} U_c(X)}$$

(2.7)

where Z is a normalizing constant that bounds the probability value to [0,1], kT is the thermal energy, c is clique in the set of cliques  $\phi$  associated with  $X_i$  and  $U_c$  is the clique energy. A typical clique in the circuit representation of Markov network will comprise of the nodes representing the inputs and output of a gate. In this sense, every gate will have its own clique and clique energy. The logic gates were represented using their sum of products term and the clique energy for each gate was derived. For an inverter with input  $x_0$  and output  $x_1$ , the clique energy was derived as follows,

$$U = -((1 - x_0)x_1 + x_0(1 - x_1))$$

=  $-(x_1 - x_0x_1 + x_0 - x_0x_1)$

=  $2x_0x_1 - x_0 - x_1$  (2.8)

The negative sign in the clique energy signified the design condition that clique energies of valid states should be lower than those of invalid states. The corresponding Gibbs distribution was given as,

$$P(x_0, x_1) = \frac{1}{Z} e^{-\frac{1}{kT}(2x_0 x_1 - x_0 - x_1)}$$

(2.9)

The probability of output  $x_1 = 1$  was calculated by marginalizing  $P(x_0, x_1)$  over all possible values of  $x_0$ .

$$P(x_{1}) = \frac{1}{Z} \sum_{x_{0} = \{0,1\}} e^{-\frac{1}{kT}(2x_{0}x_{1} - x_{0} - x_{1})}$$

$$= \frac{e^{\frac{x_{1}}{kT}} + e^{\frac{(1-x_{1})}{kT}}}{2(1 + e^{\frac{1}{kT}})}$$

(2.10)

Likewise, the probability distribution of every signal in the circuit was represented using Gibbs distribution. Corresponding probability distributions for the primary outputs of the circuit was determined by propagating the marginalized distributions across various cliques using belief propagation algorithm. Since these distributions were associated with thermal energy kT, comprehensive reliability studies on nanoarchitectures working under critical thermal limits, were performed by altering the kT values and examining the signal probability distributions. Although, this work provided some much needed insight on thermal behavior of nano-domain circuits, it was performed on error free devices instead of erroneous ones.

Another work on reliability studies using probabilistic model checking was proposed in [58]. This method employed discrete-time Markov Chains for probabilistic model checking. In another significant work [99], the average output error in digital circuits was calculated using a probabilistic reliability model that employed Bayesian Networks.

#### 2.2.3 Error Reduction Through Redundancy

The term 'redundancy' means the usage of multiple redundant copies of the same erroneous component in order to test or improve its reliability. Von Neumann, in his legendary work, was one of the first to propose one such methodology called *multiplexing* and he used it to study the reliability of NAND logic [1]. This model was created by taking multiple copies of the same erroneous NAND gate and supplying them input signals randomly from various bundles of input lines. This setup ensures effective duplication of all possible signals at the outputs. To obtain better error tolerance, two more NAND multiplexing setups are cascaded with the previous one. While the first NAND multiplexing setup called the "Executive Unit" performed the logic computation, the following two units called the "Restorative Unit" restored the correct computation values. (Fig. 2.2.)

Von Neumann also introduced the widely used redundancy technique called Triple Modular Redundancy (TMR) [1]. In TMR, three copies of the same erroneous logic component

19

Figure 2.2. NAND multiplexing scheme introduced by Von Neumann [1]

was created and the correct value was determined by performing the majority voting out of the three outputs. Given three different signals X, Y and Z, the majority voting could be performed using the function, XY + YZ + XZ. Using this, Von Neumann showed significant reduction in the probability of error occurrence in logic devices. As an extension of TMR, a more general model called N-Modular Redundancy (NMR) [2] was proposed, where N is chosen to be odd to facilitate majority voting. If TMR was used to choose the majority of 2 out of 3 inputs, NMR was used to choose the majority of n + 1 out of 2n + 1 inputs. Also, given an erroneous system with error probability  $\varepsilon$ , the reliability R through performing TMR was given by,

$$R(TMR) = \varepsilon^3 + 3\varepsilon^2(1 - \varepsilon) \tag{2.11}$$

and the corresponding reliability through performing NMR was given by,

$$R(NMR) = \sum_{i=0}^{n} \frac{N!}{(N-i)!i!} (1-\epsilon)^{i} \epsilon^{N-i}$$

(2.12)

where N = 2n + 1. These base models for hardware redundancy were later applied in essential applications like fault-tolerant microprocessor design [10], and also paved the way to a variety of techniques for software, data and time redundancies. Apart from being used in the circuit level, they were also used in different levels of design abstractions like in [73], where Selective TMR (STMR) was used in FPGA's to minimize error behavior due to SEUs.

From the initial works of Von Neumann, the study of fault-tolerant computation expanded its barriers into fields like nano-computing architectures. An expansion of the TMR technique called Cascaded Triple Modular Redundancy (CTMR) [11] was used for reliability studies of nanochips using single-electron devices and quantum cellular automata gates. While TMR is referred to as single level redundancy technique, CTMR is referred to as multilevel redundancy technique, where outputs from three different TMR units were supplied to another majority gate to perform multiple levels of voting in order to obtain better error reduction. A generalized CTMR technique, called Cascaded General Modular Redundancy (CGMR) was also proposed in this work [11].

In [12], the reliability of reconfigurable architectures was obtained using NAND multiplexing technique. The processors in the architecture were implemented with NAND multiplexing system with a redundancy factor of 3. In the design, redundant spare circuitries were also developed to enhance error correction and minimize error detection. In [13], majority multiplexing was used to achieve fault-tolerant designs for nanoarchitectures. They further enhanced the majority multiplexing model for small input error probabilities, by removing the restorative stage, since effective restoration is possible without that stage. A recent comparative study of some of these methods [14], indicates that a 1000-fold redundancy would be required for a device error (or failure) rate of  $0.01^1$ .

<sup>&</sup>lt;sup>1</sup>Note that this does *not* mean 1 out of 100 devices will fail, it indicates the devices will generate erroneous output 1 out of 100 times.

Figure 2.3. Some of the related works on reliability models for dynamic errors in VLSI circuits

#### 2.3 Relation to State-of-the-Art

This work concentrates on the following,

- Modeling *dynamic errors*, which are global, as opposed to localized SEUs. This is done using a probabilistic error model, where efficient error incorporation in multiple nodes is possible. Also in this model, the error injection and probability of error for each gate can be modified easily. Moreover, both fixed and variable gate errors can be accommodated in a single circuit without affecting computational complexity.

- Estimation of *maximum error as opposed to average error*, since for higher design levels it is important to account for maximum error behavior, especially if this behavior is far worse than the average case behavior. This estimation is performed as a diagnostic study in our error model, using the Maximum *a posteriori* (MAP) hypothesis, where the

output nodes are forced to be erroneous and the information is propagated towards the input nodes to estimate the possible input configuration, that can provide a maximum error in the output.

- Estimation of output error in *sequential circuits as opposed to combinational circuits*, since the transient errors that occurs in a particular time frame, of a sequential circuit, will propagate to consecutive time frames thereby making the device more vulnerable. This estimation is performed using a *minimal* time evolving probabilistic network, namely, the Temporal Dependency Model (TDM), that can handle both spatial dependencies between nodes in a single time slice and temporal dependencies between nodes in different time slices.

- Designing *temporal, spatial and hybrid redundancy schemes*, using our probabilistic error model, to achieve error mitigation. We perform temporal redundancy using Triple Temporal Redundancy (TTR) technique and spatial redundancy using CTMR technique. Also efficient error reduction is achieved through *selective* redundancy, by applying redundancy only to the most influential input combinations and the most sensitive nodes.

## CHAPTER 3

# **DESIGN FUNDAMENTALS**

## 3.1 Probabilistic Representation of Digital Circuits

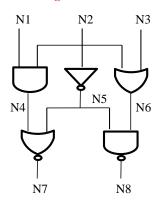

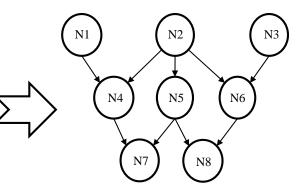

A digital circuit is basically a network of digital signals connected together through gates whose functionalities are based on boolean logic. This network can be represented accurately using a graphical model, where the nodes represent the digital signals and the edges represent the boolean logic functionality of the gates. Also these edges should be unidirectional, since information flow in digital circuits is unidirectional from input to output. In order to assist efficient diagnostic studies on digital circuits, their graphical representation can be modeled as probabilistic graphical models where each node is a random variable with two possible states, 'logic 0' and 'logic 1' or simply '0' and '1'. To represent the digital functionalities, each random variable should be associated with a probability distribution function (pdf). Consider the example in Fig 3.1., where a digital circuit and its probabilistic graphical model are given. As discussed, each node from N1 to N8 is a random variable whose value will be either '0' or '1'. In a network representing any digital circuit, the nodes corresponding to the primary inputs (i.e., N1, N2, N3 in our example) will always be completely independent and every other *child* node will be dependent on at least one *parent* node. This kind of interdependency between nodes gives rise to conditional probability distribution, and so the pdf's are represented as Conditional Probabilistic Tables (CPTs). Fig 3.1. provides the CPTs for all the nodes. Since N1, N2, N3 are primary inputs, their pdf's can be controlled by the user. The child node N4is dependent on its parent nodes N1 and N2 through AND logic, and the corresponding CPT

**Digital Circuit**

**Corresponding Probabilistic Graph model**

Digital signals governed by Boolean logic

Corresponding Conditional Probabilistic Tables (CPTs) for the graph

Figure 3.1. Representation of a digital circuit as a probabilistic graph

25

should reflect this functionality. This can be achieved by providing the pdf as follows,

$$P(N4 = 0|N1, N2) = \begin{cases} 0 & \text{if } N1 = 1 \text{ and } N2 = 1\\ 1 & \text{otherwise} \end{cases}$$

$$P(N4 = 1|N1, N2) = \begin{cases} 1 & \text{if } N1 = 1 \text{ and } N2 = 1\\ 0 & \text{otherwise} \end{cases}$$

(3.1)

Similarly the CPTs for *N5* should obey NOT logic, *N6* should obey OR logic, *N7* should obey NOR logic, and *N8* should obey NAND logic.

Once the graph model for a digital circuit is ready, the next obvious question is whether the model captures all the interdependencies between the nodes. For example, in the probabilistic graph given in Fig 3.1., the node N7 is directly dependent on nodes N4, N5 and indirectly dependent on nodes N1, N2. Also, node N8 is directly dependent on nodes N5, N6 and indirectly dependent on nodes N2, N3. If we add edges representing these indirect dependencies, then the resulting probabilistic graph will be as seen in Fig 3.2.(a). But are these edges necessary? In the given digital circuit, it can be seen that the relation of the signal N7 towards the signals N1, N2 is taken care by the signals N4, N5, i.e. any change in signals N1, N2 will be captured by their direct output signals N4, N5 and the same changes will be translated to signal N7 through N4 and N5. So, in the corresponding probabilistic graph model, we can comfortably say that node N7 is independent of nodes N1, N2 given nodes N4, N5. In a similar fashion, we can also say that node N8 is independent of nodes N2, N3 given nodes N5, N6. In other words, we can say that all the indirect dependencies are taken care by the direct dependencies. As a result all the extra edges representing indirect dependencies can be removed from the probabilistic graph model given in Fig 3.2.(a) resulting in Fig 3.2.(b), which is similar to the initial model given in Fig 3.1. This representation is the absolute *minimal*, in the sense that

**Minimal representation**

Figure 3.2. Minimal representation of the probabilistic graph

removing even one edge will collapse the interdependencies between the nodes and eventually results in an incomplete representation of the given digital circuit.

The probabilistic graph model can be represented mathematically as the conditional factoring of a joint probability distribution. Any probability function  $P(y_1, y_2, \dots, y_N)$  can be written as,

$$P(y_{1}, \dots, y_{N}) = P(y_{N}|y_{N-1}, y_{N-2}, \dots, y_{1})$$

$$P(y_{N-1}|y_{N-2}, y_{N-3}, \dots, y_{1})$$

$$\dots P(y_{1})$$

(3.2)

where  $y_1, y_2, \dots, y_N$  are random variables. This expression holds for any ordering of these random variables. For the example probabilistic graph model in Fig 3.1., this probability

function can be written as,

$$P(n1, \dots, n8) = P(n8|n7, n6, n5, n4, n3, n2, n1)$$

$$P(n7|n6, n5, n4, n3, n2, n1)$$

$$P(n6|n5, n4, n3, n2, n1)$$

$$P(n5|n4, n3, n2, n1)$$

$$P(n4|n3, n2, n1)$$

$$P(n3)P(n2)P(n1)$$

(3.3)

where  $n1, \dots, n8$  are the random variables represented by the nodes  $N1, \dots, N8$  respectively. But this equation does not perfectly represent the structure of the corresponding probabilistic graph model. As discussed earlier, in the minimal representation of the probabilistic graph model, every child node is connected only to its parent nodes. So Eqn. 3.2 can be restructured as follows,

$$P(y_1, \cdots, y_N) = \prod_{\nu} P(y_{\nu} | Pa(Y_{\nu}))$$

(3.4)

where  $Pa(Y_v)$  are the parents of the node  $Y_v$ , representing its direct causes. For the example probabilistic graph model in Fig 3.1., this restructured joint probability function can be written as,

$$P(n1, \dots, n8) = P(n8|n6, n5)P(n7|n5, n4)$$

$$P(n6|n3, n2)P(n5|n2)$$

$$P(n4|n2, n1)P(n3)P(n2)P(n1)$$

(3.5)

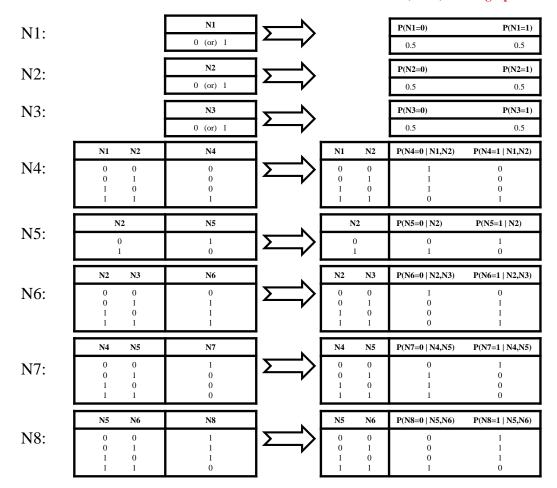

### 3.2 Modeling Error in Digital Circuits

Any unexpected change in the logic state of the digital signals gives rise to error in digital circuits. In order to understand and study these errors, we need a model that can detect these unexpected changes. One such way of doing that is to compare the erroneous circuit with its ideal error-free counterpart. Consider the circuit in Fig 3.3.(a), where each signal other than the primary input signals can be erroneous through the faulty gates. Note that we assume that primary input signals are error-free. In order to create the error detection model, two copies of the circuit is created, where one copy represents the circuit in its normal erroneous form and the other copy represents the circuit in its ideal form. When the primary outputs of these two copies are compared, any error occurrence will become evident through the possible presence of dissimilar logic states. The appropriate logic gate to do this operation is the XOR gate, which produces a '1' in its output when its inputs have dissimilar logic states and provides a '0' in its output when its inputs have similar logic states. Fig 3.3.(b) illustrates the error detection model for digital circuits based on the above mentioned concept.  $N4^e, N5^e, \dots, N8^e$  are the erroneous signals and  $N4, N5, \dots, N8$  are the ideal signals. Signal C1 gives the comparison between the erroneous and ideal primary outputs N7 and  $N7^e$ ; signal C2 gives the comparison between the erroneous and ideal primary outputs N8 and  $N8^{e}$ . It should be noted that the ideal error-free portion and the comparator portion are fictitious and used only for studying the given circuit.

The corresponding probabilistic graph model for error detection can be created as shown in Fig 3.3.(d). Lets say that each gate in the digital circuit has  $\varepsilon$  % chance of being faulty.  $\varepsilon$ can be termed as the *gate error probability*. This can be accommodated in the corresponding

Figure 3.3. Error model

www.manaraa.com

Figure 3.4. Conditional probabilistic tables for the ideal and erroneous nodes in the error model

probabilistic graph model by changing the CPTs as follows,

$$P(N4^{e} = 0|N1, N2) = \begin{cases} \epsilon & \text{if } N1 = 1 \text{ and } N2 = 1\\ 1 - \epsilon & \text{otherwise} \end{cases}$$

$$P(N4^{e} = 1|N1, N2) = \begin{cases} 1 - \epsilon & \text{if } N1 = 1 \text{ and } N2 = 1\\ \epsilon & \text{otherwise} \end{cases}$$

(3.6)

where  $N4^e$  is the erroneous output signal of a faulty AND gate as shown in Fig 3.3.(a). Accordingly, the corresponding CPTs for rest of the erroneous nodes are provided in Fig 3.4.

### **CHAPTER 4**

## MAXIMUM ERROR MODELING

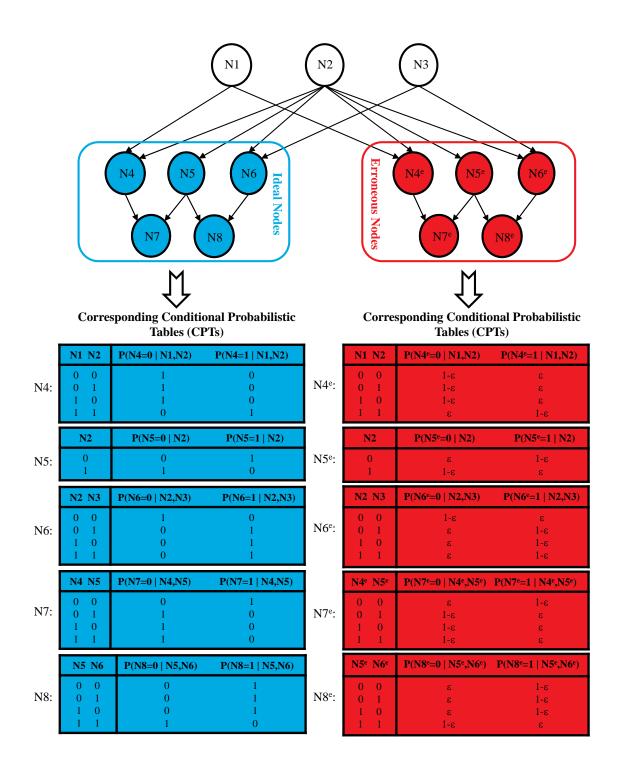

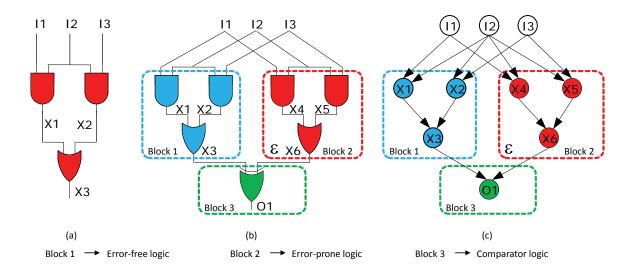

In this chapter, we present a probabilistic model to study the *maximum* output error over all possible input space for a given logic circuit. We present a method to find out the worst-case input vector, i.e., the input vector that has the highest probability to give an error at the output. In the first step of our model, we convert the circuit into a corresponding *edge-minimal* probabilistic network that represents the basic logic function of the circuit by handling the interdependencies between the signals using random variables of interest in a composite joint probability distribution function  $P(y_1, y_2, \dots, y_N)$ . Each node in this network corresponds to a random variable representing a signal in the digital circuit, and each edge corresponds to the logic governing the connected signals. The individual probability distribution for each node is given using conditional probability tables.

From this probabilistic network we obtain our probabilistic error model that consists of three blocks, (i) ideal error free logic, (ii) error prone logic where every gate has a gate error probability  $\varepsilon$  i.e., each gate can go wrong individually by a probabilistic factor  $\varepsilon$  and (iii) a detection unit that uses comparators to compare the error free and erroneous outputs. The error prone logic represents the real time circuit under test, whereas the ideal logic and the detection unit are fictitious elements used to study the circuit. Both the ideal logic and error prone logic would be fed by the primary inputs **I**. We denote all the internal nodes, both in the error free and erroneous portions, by **X** and the comparator outputs as **O**. The comparators are based on XOR logic and hence a state "1" would signify error at the output. An evidence set **o** is created by evidencing one or more of the variables in the comparator set **O** to state "1" ( $P(O_i = 1) =$

1). Then performing MAP hypothesis on the probabilistic error model provides the worstcase input vector  $\mathbf{i}_{MAP}$  which gives  $\max_{\forall \mathbf{i}} P(\mathbf{i}, \mathbf{o})$ . The maximum output error probability can be obtained from  $P(O_i = 1)$  after instantiating the input nodes of probabilistic error model with  $\mathbf{i}_{MAP}$  and inferencing. The process is repeated for increasing  $\varepsilon$  values and finally the  $\varepsilon$  value that makes at least one of the output signals completely random ( $P(O_i = 0) = 0.5$ ,  $P(O_i = 1) = 0.5$ ) is taken as the error bound for the given circuit.

It is obvious that we can arrive at MAP estimate by enumerating all possible input instantiations and compute the maximum  $P(\mathbf{i}, \mathbf{o})$  by any probabilistic computing tool. The attractive feature of this MAP algorithm lies on eliminating a significant part of the input search-subtree based on an easily available upper-bound of  $P(\mathbf{i}, \mathbf{o})$  by using probabilistic traversal of a binary Join tree with *Shenoy-Shafer* algorithm [23, 24]. The actual computation is divided into two theoretical components. First, we convert the circuit structure into a binary Join tree and employ Shenoy-Shafer algorithm, which is a two-pass probabilistic message-passing algorithm, to obtain multitude of upper bounds of  $P(\mathbf{i}, \mathbf{o})$  with partial input instantiations. Next, we construct a Binary tree of the input vector space where each path from the root node to the leaf node represents an input vector. At every node, we traverse the search tree if the upper bound, obtained by Shenoy-Shafer inference on the binary join tree, is greater than the maximum probability already achieved; otherwise we prune the entire sub-tree. Experimental results on a few standard benchmark show that the worst-case errors significantly deviate from the average ones and also provides tighter bounds for the ones that use homogeneous gate-type (c17 with NAND-only). Salient features and deliverables are itemized below:

• We have proposed a method to calculate *maximum* output error using a probabilistic model. Through experimental results, we show the importance of modeling maximum output error. (Fig. 4.10.)

34

- Given a circuit with a fixed gate error probability ε, our model can provide the maximum output error probability and the *worst-case* input vector, which can be very useful testing parameters.

- We present the circuit-specific error bounds for fault-tolerant computation and we show that maximum output errors provide a tighter bound.

- We have used an efficient design framework that employs inference in binary join trees using Shenoy-Shafer algorithm to perform MAP hypothesis accurately.

- We give a probabilistic error model, where efficient error incorporation is possible, for useful reliability studies. Using our model the error injection and probability of error for each gate can be modified easily. Moreover, we can accommodate both fixed and variable gate errors in a single circuit without affecting computational complexity.

We would like the readers to note that we will be representing a set of variables by bold capital letters, set of instantiations by bold small letters, any single variable by capital letters. Also probability of the event  $Y_i = y_i$  will be denoted simply by  $P(y_i)$  or by  $P(Y_i = y_i)$ .

# 4.1 Maximum a Posteriori (MAP) Estimate

Let us define the random variables in our probabilistic error model as  $Y = I \cup X \cup O$ , composed of the three disjoint subsets I, X and O where

- $I_1, \dots, I_k \in \mathbf{I}$  are the set of k primary inputs.

- *X*<sub>1</sub>, · · · , *X<sub>m</sub>* ∈ **X** are the *m* internal logic signals for both the erroneous (every gate has a failure probability ε) and error-free ideal logic elements.

- *O*<sub>1</sub>, · · · , *O<sub>n</sub>* ∈ **O** are the *n* comparator outputs, each one signifying the error in one of the primary outputs of the logic block.

Figure 4.1. (a) Digital logic circuit (b) Error model (c) Probabilistic error model

• N = k + m + n is the total number of network random variables.

Any primary output node can be forced to be erroneous by fixing the corresponding comparator output to logic "1", that is providing an evidence  $\mathbf{o} = \{P(O_i = 1) = 1\}$  to a comparator output  $O_i$ . Given some evidence  $\mathbf{o}$ , the objective of the Maximum *a posteriori* estimate is to find a complete instantiation  $\mathbf{i}_{MAP}$  of the variables in  $\mathbf{I}$  that gives the following joint probability,

$$MAP(\mathbf{i}_{MAP}, \mathbf{o}) = \max_{\forall \mathbf{i}} P(\mathbf{i}, \mathbf{o})$$

(4.1)

The probability  $MAP(\mathbf{i}_{MAP}, \mathbf{o})$  is termed as the *MAP probability* and the variables in **I** are termed as *MAP variables* and the instantiation  $\mathbf{i}_{MAP}$  which gives the maximum  $P(\mathbf{i}, \mathbf{o})$  is termed as the *MAP instantiation*.

For example, consider Fig 4.1. In the probabilistic model shown in Fig 4.1.(c), we have  $\{I1, I2, I3\} \in \mathbf{I}; \{X1, X2, X3, X4, X5, X6\} \in \mathbf{X}; \{O1\} \in \mathbf{O}. X3$  is the ideal error-free primary output node and *X*6 is the corresponding error-prone primary output node. Giving an evidence  $\mathbf{o} = \{P(O1 = 1) = 1\}$  to *O*1 indicates that *X*6 has produced an erroneous output. The MAP hypothesis uses this information and finds the input instantiation,  $\mathbf{i}_{MAP}$ , that would give the

maximum  $P(\mathbf{i}, \mathbf{o})$ . This indicates that  $\mathbf{i}_{MAP}$  is the most probable input instantiation that would give an error in the error-prone primary output signal X6. In this case,  $\mathbf{i}_{MAP} = \{I1 = 0, I2 = 0, I3 = 0\}$ . This means that the input instantiation  $\{I1 = 0, I2 = 0, I3 = 0\}$  will most probably provide a wrong output, X6 = 1 (since the correct output is X6 = 0).